# Schmalbandige nichtlineare Optimierung des Gate-Ansteuerungssignals von Leistungstransistoren zur Minimierung von Schaltresonanzen

M.Sc. Caroline Krause, Prof. Dr.-Ing. Stephan Frei, Technische Universität Dortmund

### 1 Einleitung

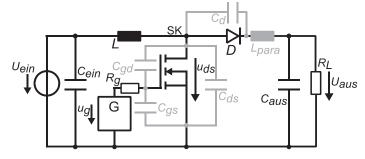

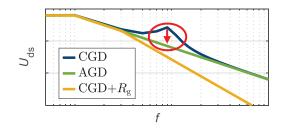

Leistungselektronische Wandler basierend auf Leistungstransistoren sind eine Hauptkomponente zur Energiewandlung und Energieverteilung. In modernen Wandlern werden Wide-Bandgap-Halbleiter, wie beispielsweise Gallium Nitrid (GaN) oder Silizium Carbid (SiC) Transistoren, verwendet, mit denen steilere Schaltflanken, mit dem Vorteil reduzierter Schaltverluste gegenüber üblichen Silizium MOSFETs (metal oxide semiconductor field effect transistor), erzielt werden können. Nachteilig kann jedoch sein, dass hochfrequente Oszillationen durch die schnellen Schaltvorgänge angeregt werden [1]. Zur Erläuterung wird ein DC-DC Aufwärtswandler, wie in Abbildung 1 dargestellt, betrachtet. Durch die Ansteuerung mit einem konventionellen Gate-Treiber (engl. conventional gate driver, CGD) mit einem näherungsweise trapezförmigen Gate-Treibersignal ergeben sich am Schaltknoten (SK) des Wandlers gedämpfte Schwingungen hoher Frequenz nach den Schaltvorgängen, die, wie in Abbildung 2 in blau dargestellt, in einem Peak im Spektrum resultieren. Verantwortlich hierfür sind parasitäre reaktive Elemente, die in Abbildung 1 in grau dargestellt sind. Die Oszillation im gesperrten Zustand des Transistors wird durch den Schwingkreis bestehend aus der parasitären Drain-Source Kapazität Cds des Transistors, der Diode, der parasitären Induktivität  $L_{para}$ , typischerweise bedingt durch das Leiterplattenlayout, sowie der Parallelschaltung aus der Ausgangskapazität  $C_{aus}$  und dem Lastwiderstand  $R_{L}$  hervorgerufen. Ein häufig verwendeter Ansatz zur Reduktion der Schwingungen ist die Verwendung eines zusätzlichen Gate-Widerstands, Rg in Abbildung 1. Hierdurch wird die Steilheit der Schaltflanken reduziert und die Schwingungen werden weniger stark angeregt (Abbildung 2 gelb). Das EMV-Verhalten verbessert sich. Andererseits werden die Schaltverluste stark durch die langsameren Schaltvorgänge erhöht. Ziel ist hier, durch die Verwendung eines flexiblen aktiven Gate-Treibers (engl. active gate driver, AGD), der ein nahezu beliebiges Ansteuerungssignal bereitstellen kann, das maximale Überschwingen von  $u_{

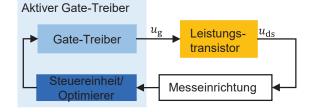

m ds}$  weiter zu reduzieren und gleichzeitig möglichst steile Schaltflanken beizubehalten, um geringe Verluste zu erzeugen. Da die Störungen im betrachteten Beispiel schmalbandig sind, wird nur der gestörte Frequenzbereich durch den AGD beeinflusst (Abbildung 2 grün). Es gilt also, ein passendes Ansteuerungssignal  $u_g$  zu finden, dass nur die Resonanz im Signal  $u_{ds}$  minimiert und ansonsten das Verhalten der Schaltung möglichst nicht beeinflusst. Da das Übertragungsverhalten zwischen  $u_{\rm q}$  und  $u_{\rm ds}$  hochgradig nichtlinear ist, muss zur Bestimmung des Signals ein geeignetes Verfahren eingesetzt werden. Der prinzipielle Ansatz der aktiven Gate-Ansteuerung ist in Abbildung 3 dargestellt. Im Wesentlichen kann der aktive Gate-Treiber in zwei Teile unterteilt werden. Zum einen in die analoge Gate-Treiber Schaltung und zum anderen in eine Steuereinheit. Unterschiedliche Ansätze zum Aufbau der analogen aktiven Gate-Treiber sind bekannt. Häufig werden hier, wie in [2] und [3] beschrieben, variable Spannungsquellen, variable Stromquellen oder Netzwerke aus variabel zuschaltbaren Widerständen verwendet. In dieser Arbeit wird als Gate-Treiberschaltung eine variable Spannungsguelle verwendet, um die in der Steuereinheit berechneten Signale an das Gate des Transistors anzulegen. Auf Basis der Drain-Source Spannung  $u_{ds}$  wird in der Steuereinheit das Gate-Signal bestimmt. Hierzu werden in der Literatur unterschiedliche Ansätze verwendet. In [4] wird das Ansteuerungssignal auf Grundlage des Ausgangskennlinienfeldes bestimmt und in [5] auf Basis der Schaltcharakteristik des Transistors. Um mit diesen Ansätzen eine gute aktive Gate-Ansteuerung realisieren zu können, bedarf es jedoch einer sehr hohen Genauigkeit der Modelle, die sehr schwer zu realisieren ist. Andere Ansätze, die keine Modelle des Systems benötigen, basieren auf Optimierungsalgorithmen. In [6], [7] und [8] werden heuristische Optimierungsalgorithmen verwendet. Nachteil heuristischer Verfahren ist jedoch, dass diese eine relativ langsame Konvergenzrate aufweisen und die Ergebnisse nicht reproduzierbar sind. Ein vielversprechenderer Ansatz ist die Verwendung deterministischer Optimierungsverfahren. In [9] wird ein Pattern-Search Algorithmus verwendet und in [10] ein Newton-Verfahren mit schrittweiser Adaption der Zielfunktion. Das Verfahren in [10] hat den Nachteil, dass die Zielfunktion für alle zu optimierenden Harmonischen des Gate-Signals einen Wert vorgeben muss. Diese Werte zu bestimmen, sodass ein physikalisches Zielsignal resultiert, erweist sich jedoch in der Praxis als sehr schwierig. Detaillierter wird auf die Problematik in [11] und in Kapitel 2.2 eingegangen.

Vor diesem Hintergrund wird in dieser Arbeit mit dem Levenberg-Marquardt-Verfahren (LMV), eine Abwandlung des Newton-Verfahrens, das Ansteuerungssignal iterativ optimiert [12]. Wie in Abbildung 2 dargestellt ist das Ziel, den Peak im Spektrum der Drain-Source Spannung zu reduzieren. Dabei soll das Gate-Signal breitbandig optimiert werden, um neben der Reduktion der Oszillation, die Verlustleistung möglichst gering zu halten. Beim LMV wird eine skalare Kostenfunktion definiert, dessen Minimum gesucht wird. Um Konvergenz zu erreichen besteht nicht wie beim Verfahren in [10] die Problematik der Notwendigkeit eines physikalischen Zielsignals bei einer breitbandigen Optimierung von  $u_g$ . Ebenso ist das Verfahren hinsichtlich der Wahl der Startwerte robuster gegenüber dem in [10] verwendeten mehrdimensionalen Newton-Verfahren.

Die Theorie der Optimierung der Drain-Source Spannung basierend auf dem LMV im Frequenz-

bereich wird in Kapitel 2 erläutert. In Kapitel 3 wird die Methode auf einen DC-DC Aufwärtswandler angewendet. Weiter wird der Einfluss der Optimierungsparameter auf das Optimierungsergebnis und die Effizienz der Optimierung analysiert und diskutiert. In Kapitel 4 werden die Ergebnisse zusammengefasst und Erweiterungsmöglichkeiten der Methode dargestellt.

Abbildung 1: Ersatzschaltbild des Aufwärtswandlers

Abbildung 2:  $U_{\rm ds}$  im Frequenzbereich bei unterschiedlichen Gate-Treiberstrategien

Abbildung 3: Allgemeine schematische Darstellung der Methode der aktiven Gate-Ansteuerung

# 2 Methode der aktiven Gate-Ansteuerung im Frequenzbereich

Im Folgenden wird die Methode zur aktiven Gate-Ansteuerung basierend auf dem Levenberg-Marquardt-Verfahren beschrieben. Die Grundlagen und Zielsetzungen zur Optimierung im Frequenzbereich werden erläutert.

# 2.1 Betrachtungen im Frequenzbereich

Aufgrund der Funktionsweise eines Aufwärtswandlers ist es nicht möglich, das notwendige Ansteuerungssignal des Gates des Transistors Zeitschritt für Zeitschritt so zu berechnen, dass ein gefordertes Zielsignal erreicht werden kann. Dies liegt darin begründet, dass durch die Pulsbreite des Gate-Signals die Ausgangsspannung des Aufwärtswandlers bestimmt wird und damit auch der Maximalwert der Drain-Source Spannung vorgegeben ist. Dieser Zusammenhang kann aber bei einer Optimierung, die Zeitschritt für Zeitschritt erfolgt, nicht berücksichtigt werden. Daher muss bei der Optimierung das gesamte Signal einer Periodendauer betrachtet werden. Darüber hinaus müssen alle transienten Vorgänge angeschlossen sein, sodass sich das System im stationären Zustand befindet. Wenn dies gegeben ist, können alle Signale auch als Fourier-Reihe

dargestellt werden. Im Folgenden werden alle Zeitbereichssignale mit dem entsprechenden Kleinbuchstaben gekennzeichnet und alle Frequenzbereichssignale, dargestellt über die Koeffizienten der Fourier-Reihe, mit den entsprechenden Großbuchstaben. Die Signale werden hier durch die komplexe Fourier-Reihe nach Gleichung (1) dargestellt

$$u(t) = \sum_{n=-\infty}^{\infty} (U_{\text{Re},n} + j U_{\text{Im},n}) \cdot e^{j2\pi n f_0 t}.$$

$$\tag{1}$$

Dabei sind  $U_{\rm Re,n}$  und  $U_{\rm Im,n}$  die Koeffizienten der Fourier-Reihe der n-ten Harmonischen, j die imaginäre Einheit,  $f_0$  die Pulswiederholfrequenz und t die Zeit.

#### 2.2 Bestimmung des Zielsignals

Zur aktiven Gate-Ansteuerung mit dem LMV ist eine Zielsignalforderung notwendig. Wie in Abbildung 2 dargestellt und in Kapitel 1 erläutert ist das Ziel, die Oszillation, beziehungsweise den hochfrequenten Peak im Spektrum der Drain-Source Spannung zu reduzieren. Das Ziel kann jedoch nicht sein, das Signal an einer Stelle zu null zu reduzieren, da dies zu einer nicht physikalischen Drain-Source Spannung führen würde. Das Zielsignal muss daher derart definiert werden, dass das Nutzsignal sich nicht zu sehr verändert. Diese Herausforderung wird in [11] thematisiert und durch die Lösung eines Constrained-Satisfaction Problems gelöst. Bei diesem Ansatz ist jedoch bereits ein hoher Rechenaufwand erforderlich, um das Zielsignal zu bestimmen. Darüber hinaus erhöhen sich hier die Verluste stark. Um den Aufwand zur Bestimmung des Ansteuerungssignals zu reduzierten, die Verluste möglichst gering zu halten und dennoch ein physikalisches Zielsignal zu erhalten, wird das im folgenden Abschnitt beschriebene Levenberg-Marquardt-Verfahren angewendet. Wird hier ein nicht-physikalisches Zielsignal gefordert, konvergiert das LMV dennoch gegen ein realisierbares Minimum.

#### 2.3 Das Levenberg-Marquardt-Verfahren

Das LMV ist ein Verfahren zur Minimierung einer Funktion mit summierten quadratischen Fehlern basierend auf dem Newton-Verfahren. Bei Minimierungsalgorithmen beruhend auf Newton-Verfahren wird immer die Ableitung der zu minimierenden Funktion benötigt. Da die Bestimmung der Ableitung in den meisten Fällen nicht analytisch möglich ist, muss diese nummerisch berechnet werden. Dies ist jedoch sehr rechenaufwändig. Um ein gutes Ergebnis der Optimierung im Zeitbereich zu erhalten, muss das Zeitbereichssignal, gerade im Bereich der Schaltflanken, sehr fein abgetastet werden. Da wie zuvor, bei einer Optimierung im Zeitberiech das gesamte Signal einer Periodendauer betrachtet werden muss, ist eine Bestimmung der Ableitung und damit verbunden die Optimierung im Zeitbereich sehr rechen- und zeitintensiv. Wird hingegen die Optimierung im Frequenzbereich durchgeführt, werden die Flanken insgesamt durch Veränderung einer Harmonischen beeinflusst. Um das Minimum durch die Optimierung bestmöglich zu erreichen, ist die Optimierung aller Harmonischen notwendig. Um nur eine schmalbandige Verbesserung zu erzielen, ist es jedoch nicht notwendig, alle Harmonischen zu optimieren. Dieser Aspekt wird im Kapitel 3.3 im Detail betrachtet. Die Optimierung von nur einem Teil der Harmonischen ermöglicht eine enorme Zeitersparnis, sodass im Folgenden die Optimierung der Drain-Source Spannung im Frequenzberiech erfolgen kann.

Zur Optimierung der Drain-Source Spannung bei der aktiven Gate-Ansteuerung wird die zu optimierende Funktion hier zu

$$F = \sum_{n=0}^{m} (|U_{ds,n}| - |U_{ds,Z,n}|)^{2}$$

(2)

formuliert. Dabei wird die Differenz zwischen dem Betrag der Fourier-Koeffizienten des aktuellen Werts der Harmonischen der Drain-Source Spannung  $|U_{\mathrm{ds,n}}|$  und dem Zielwert des Betrags der jeweiligen Harmonischen  $|U_{\mathrm{ds,Z,n}}|$  quadriert und anschließend über alle Frequenzen über den Laufindex n der Summe von 0 Hz bis  $(m \cdot f_0)$  Hz aufsummiert. Das Vorgehen beim LMV ist in

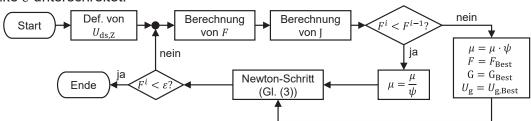

Abbildung 4 schematisch dargestellt. Die Kostenfunktion F wird hier durch Anpassung des Gate-Signals  $U_g$  im Iterationsschritt i durch die Iterationsvorschrift in Gleichung (3)

$$U_g^i = U_g^{i-1} - (G \cdot G^T + \mu \cdot \mathbf{I})^{-1} \cdot J \cdot F$$

(3)

mit dem Gradienten G, der Einheitsmatrix I und dem Skalierungsfaktor  $\mu$  minimiert. Beim LMV nach [12] wird die Hesse-Matrix durch  $\mathbf{H} = \mathbf{G} \cdot \mathbf{G}^T$  approximiert, um den hohen Rechenaufwand der Bestimmung der Hesse-Matrix zu reduzieren. Da die approximierte Hesse-Matrix jedoch nicht zwingend invertierbar ist, wird die Einheitsmatrix I gewichtet mit dem Skalierungsfaktor  $\mu$ , zu dieser hinzuaddiert. Daraus folgt, dass durch passende Wahl des Skalierungsfaktors  $\mu$  die Matrix immer invertierbar und positiv definit ist, sodass die Lösung in Richtung eines Minimums der Kostenfunktion konvergiert. In jedem Iterationsschritt wird der Skalierungsfaktor angepasst. Dies erfolgt in Abhängigkeit der zu optimierenden Funktion. Ist die Funktion im aktuellen Iterationsschritt kleiner als im vorherigen Iterationsschritt, so wird  $\mu$  verringert durch Division durch den Parameter  $\psi$ . Ist der Wert der Funktion größer, wird  $\mu$  durch Multiplikation mit  $\psi$  erhöht, die Funktion F, der Gradient G und das Gate-Signal G0 bekommen die Werte zugehörig zur zuvor besten Funktion F1 zugewiesen. Für sehr große Werte von  $\mu$ 1 wird der Einfluss der approximierten Hesse-Matrix vernachlässigbar klein und die Iterationsvorschrift aus Gleichung (3) geht über zu

$$U_g^i = U_g^{i-1} - \frac{1}{\mu} \cdot G \cdot F. \tag{4}$$

Für sehr kleine Werte von  $\mu$  geht das Verfahren in das Gauß-Newton Verfahren über [12]. Zur Bestimmung des Gradienten wird die Funktion F nach allen zu optimierenden Harmonischen des Gate-Signals abgeleitet. Der Gradient G ergibt sich damit zu

$$G = \begin{bmatrix} \frac{\partial F}{\partial U_{g,0}} & \frac{\partial F}{\partial U_{g,Re,1}} & \frac{\partial F}{\partial U_{g,Im,1}} & ... & \frac{\partial F}{\partial U_{g,Re,m}} & \frac{\partial F}{\partial U_{g,Im,m}} \end{bmatrix}^T. \tag{5}$$

Der gesamte Optimierungsschritt wird iterativ so lange wiederholt, bis die maximale Anzahl zuge-

Der gesamte Optimierungsschritt wird iterativ so lange wiederholt, bis die maximale Anzahl zugelassener Iterationen erreicht ist oder bis der Wert der zu optimierenden Funktion die obere Schranke  $\varepsilon$  unterschreitet.

Abbildung 4: Flussdiagramm des verwendeten Levenberg-Marquardt-Verfahrens

#### 3 Anwendung der aktiven Gate-Ansteuerung auf einen Aufwärtswandler

Im folgenden Abschnitt wird das zuvor beschriebene Levenberg-Marquardt-Verfahren zur Ansteuerung eines Transistors in einem DC-DC Aufwärtswandler angewendet. Zunächst wird das verwendete Testsystem erläutert und optimiert. Anschließend werden die Optimierungsparameter analysiert und diskutiert.

# 3.1 Testsystem des DC-DC Aufwärtswandlers

Nachfolgend wird der in Abbildung 1 dargestellte DC-DC Aufwärtswandler näher betrachtet. Die DC-Eingangsspannung  $U_{\rm ein}$  von 12 V wird durch Schalten des Transistors mit einer Schaltfrequenz von 1 MHz und einer Pulsbreite von 50 % und einer Anstiegs- und Abfallzeit von 5 ns auf eine Ausgangsspannung  $U_{\rm aus}$  von 24 V gewandelt. Als Transistormodell wird das ideale Modell eines GaN-HEMTs (EPC2020 [13]) verwendet. Darüber hinaus werden die parasitäre Gate-Drain  $C_{\rm gd}$ , Gate-Source  $C_{\rm gs}$  und Drain-Source Kapazität  $C_{\rm ds}$  berücksichtigt. Die Pufferkondensatoren  $C_{\rm ein}$  und  $C_{\rm aus}$  werden zu 22  $\mu$ F gewählt und die Speicherinduktivität L zu 2,35  $\mu$ H. Der aktive Gate-Treiber besteht aus einer Signalquelle und einem Widerstand  $R_{\rm g}$  von 5  $\Omega$ . Als Diode wird das

Modell einer idealen Diode verwendet mit einer parallelen parasitären Kapazität. Zwischen Diode und Ausgang des Wandlers wird eine parasitäre Induktivität von 20 nH berücksichtigt.

#### 3.2 Optimierung der hochfrequenten Störungen

Der zuvor beschriebene Testaufbau wird nachfolgend in einer Simulation zur Validierung des vorgestellten Ansatzes der aktiven Gate-Ansteuerung verwendet. Im ersten Schritt wird der Transistor wie meist üblich über ein Signal mit gaußförmigen Flanken angesteuert. Dieses Signal ist in Abbildung 5 in blau im Zeit- und Frequenzbereich dargestellt. Es resultiert das in Abbildung 6 ebenfalls in blau dargestellte Signal der Drain-Source Spannung im Zeit- und Frequenzbereich. Die gedämpfte Schwingung nach dem Ausschaltvorgang ist im Zeitbereichssignal gut erkennbar. Die resultierende Überhöhung im Frequenzbereich tritt bei der Grundfrequenz der Schwingung auf. Darüber hinaus erhöhen sich die Amplituden in einem schmalbandigen Bereich um die Grundfrequenz der Schwingung. Bei ca. 35 MHz tritt ein Peak im Spektrum auf. Wird die Amplitude der Grundschwingung reduziert, so reduzieren sich gleichzeitig die Amplituden der zum Peak benachbarten Harmonischen. Es genügt daher als Zielvorgabe, die Harmonische bei 35 MHz zu reduzieren. Damit die Oszillation im Zeitbereich möglichst gering wird, wird eine Reduktion der Harmonischen um 20 dB angestrebt. Gleichung (2) kann hier auf Gleichung (6),

$$F = (|U_{ds,35}| - |U_{ds,Z,35}|)^2, \tag{6}$$

$F = \left(|U_{\rm ds,35}| - |U_{\rm ds,Z,35}|\right)^2, \tag{6}$  reduziert werden. Der Wert von  $|U_{\rm ds,Z,35}|$  soll also um 20 dB unter dem Wert der ursprünglichen Harmonischen bei 35 MHz liegen. In Abbildung 6 ist das Optimierungsziel in gelb dargestellt. Die Optimierung wird für 5001 Frequenzen, von 0 Hz bis 5 GHz durchgeführt, sodass 10001 Fourier-Reihenkoeffizienten optimiert werden. Diese Freguenzauflösung ist erforderlich, damit das Zeitbereichssignal ausreichend genau simuliert werden kann. Zur Bestimmung des Gradienten G sind demnach in jedem Iterationsschritt 20002 Simulationen erforderlich, wenn die Ableitung der Kostenfunktion nach jedem Fourier-Koeffizienten des Gate-Signals, hier beispielsweise für den Realteil der n-ten Harmonischen, mit zentralen Differenzen nach Gleichung (7)

$$\frac{\partial F}{\partial U_{\rm g,n}} = \frac{F\big(U_{\rm g,n} + \Delta U\big) - F\big(U_{\rm g,n} - \Delta U\big)}{2 \cdot \Delta U} \tag{7}$$

berechnet wird. Dazu wird die zu optimierende Funktion jeweils in Abhängigkeit der Erhöhung

beziehungsweise der Reduktion um  $\Delta U$  des entsprechenden Fourier-Koeffizienten von  $U_g$  bestimmt, wobei  $\Delta U$  hier zu  $10^{-5}$  gewählt wird. Hiermit wird die Approximation der Hesse-Matrix bestimmt und auf Grundlage des Werts der Optimierungsfunktion im vorherigen Iterationsschritt der Wert von  $\mu$  angepasst. Als Startwert wird der Skalierungsfaktor  $\mu$  zu 30 und der Parameter  $\psi$ zu 10 gewählt.

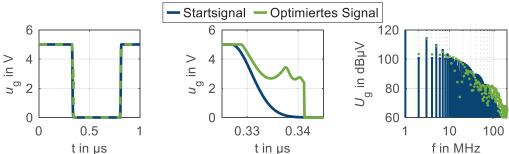

Abbildung 5: Startsignal und optimiertes Signal der Gate-Spannung im Zeitbereich (links und Zoom in der Mitte) und im Frequenzbereich (rechts)

Durch die Änderung der Fourier-Koeffizienten kommt es dazu, dass sich das Gate-Signal im einund ausgeschalteten Zustand des Transistors ändert. Durch das hochgradig nichtlineare Übertragungsverhalten des Transistors haben diese Änderungen jedoch nur einen vernachlässigbaren Einfluss auf die Drain-Source Spannung. Darüber hinaus kann es dazu kommen, dass die minimal und maximal zulässige Spannung am Gate des Transistors hierdurch über- oder unterschritten wird. Aus diesen Gründen wird das Gate-Signal außerhalb des Bereichs der Schaltflanken hier auf eine obere Schranke von 5 V und eine untere Schranke von 0 V begrenzt. Die beschriebene Optimierung wird so lange durchgeführt bis der Wert der Kostenfunktion die obere Schranke von  $\varepsilon=10^{-9}$  unterschreitet oder bis maximal 100 Iterationsschritte durchgeführt wurden. Das aus der Optimierung resultierende Gate-Ansteuerungssignal ist in Abbildung 5 in grün dargestellt. Die resultierende Drain-Source Spannung ist in Abbildung 6 ebenfalls in grün im Zeit- und Frequenzbereich dargestellt. Die geforderte Reduktion der Harmonischen bei 35 MHz wird erreicht und das maximale Überschwingen im Zeitbereich reduziert sich von 34,6 V auf 26,0 V.

Abbildung 6: Startsignal, Zielsignal und optimiertes Signal der Drain-Source Spannung im Zeitbereich (oben) und im Frequenzbereich (unten); links: vollständiger optimierter Bereich, rechts: Zoom

# 3.3 Analyse der Optimierungsparameter

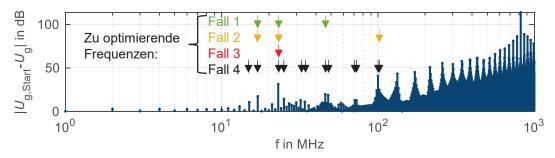

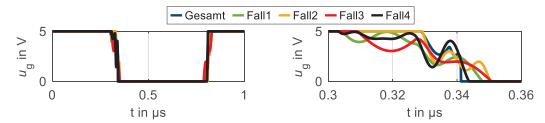

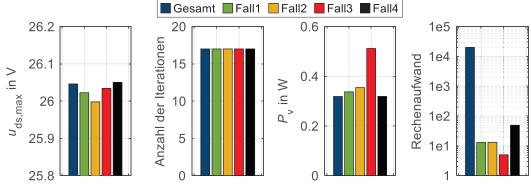

Wie zuvor erwähnt, bedarf die Optimierung in jedem Optimierungsschritt im obigen Beispiel 20002 Simulationen für die Bestimmung des Gradienten und einer Simulation zur Bestimmung der Optimierungsfunktion. Es entsteht ein sehr hoher Rechenaufwand und die Optimierung wird sehr zeitintensiv. Aufgrund der Signalform des Ansteuerungssignals im Bereich der Flanken liegt es nahe, dass eine Reduktion der Oszillation auch durch die Optimierung von weniger Harmonischen des Gate-Signals erzielt werden kann. Dies wird im Folgenden untersucht. Der Einfluss auf das resultierenden maximalen Überschwingen, auf die Verlustleistung, die benötigte Anzahl an Iterationen und den Rechenaufwand wird bewertet. Als Maß für den Rechenaufwand wird die notwendige Anzahl von Simulationen in jedem Iterationsschritt herangezogen. Im zuvor genannten Beispiel liegt der Rechenaufwand beispielsweise bei 20003 Simulationen. Um das erforderliche optimierte Ansteuerungssignal, ausgehend vom ursprünglichen trapezförmigen Ansteuerungssignal durch Optimierung von weniger Harmonischen approximieren zu können, wird zunächst der Betrag der Differenz der Betragsspektren des Gate-Startsignals und des optimierten Gate-Signals betrachtet. Dies ist in Abbildung 7 dargestellt. Es ist zu erkennen, dass einzelne Harmonische stärker verändert werden. Vor diesem Hintergrund werden die vier durch die unterschiedlichen Farben gekennzeichneten Fälle näher betrachtet. Es werden sich stark ändernden Harmonischen unterhalb von 100 MHz optimiert, um das Ansteuerungssignal bei der Optimierung des gesamten Spektrums im Bereich der Flanken nachzubilden. Dazu werden die Anzahlen und die Frequenzen der optimierten Harmonischen variiert. Alle mit einem Pfeil in der jeweils gleichen Farbe gekennzeichneten Harmonischen werden dabei in den unterschiedlichen Szenarien optimiert. Dazu wird ebenso das LMV verwendet mit der gleichen Zielvorgabe, die Harmonische der Drain-Source Spannung bei 35 MHz um 20 dB zu reduzieren. Die resultierenden optimierten Gate-Signale sind in Abbildung 8 dargestellt. In allen Fällen wird die Zielvorgabe an die Drain-Source Spannung hinreichend genau erfüllt. Durch die Optimierung der Harmonischen im Fall 4 wird im Zeitbereich das Signal der fallenden Schaltflanke des Gate-Signals am besten nachgebildet. Die mittlere Verlustleistung und das maximale Überschwingen ändern sich nur minimal. Dies ist in Abbildung 9 zu erkennen. Hier sind die Gütekriterien für alle betrachteten Fälle dargestellt. In allen Fällen wurde der Rechenaufwand stark gegenüber der Optimierung aus Kapitel 3.2 reduziert. Die benötigte Anzahl an Iterationen ändert sich jedoch nicht. Das maximale Überschwingen bleibt ebenso näherungsweise gleich und wird in den Fällen 1 bis 3 sogar minimal kleiner. Bei Betrachtung der mittleren Verlustleistung ist zu erkennen, dass diese in allen Fällen im Vergleich zur mittleren Verlustleistung der Optimierung aller Harmonischer ansteigt, jedoch nur im dargestellten Fall 3 mit einer wesentlichen Erhöhung der mittleren Verlustleistung. Bei Optimierung einer einzelnen Harmonischen in den betrachteten Fällen lässt die Güte der Optimierung am stärksten nach, sodass für einen besseren Kompromiss zwischen EMV-Verhalten und Verlustleistung die Optimierung mehrerer Harmonischer vorteilhaft ist. Zusammenfassend lässt sich festhalten, dass die Güte der Optimierung zur aktiven Gate-Ansteuerung bei geeigneter Wahl der optimierten Harmonischen des Gate-Signals beibehalten wird und der Rechenaufwand sowie der nötige Zeitbedarf der Optimierung stark reduziert werden kann.

Abbildung 7: Differenz des Startsignals und des optimierten Signals der Gate-Spannung im Frequenzbereich

Abbildung 8: Optimierte Gate-Signale in Abhängigkeit der Optimierung unterschiedlicher Harmonischer

Abbildung 9: Rechenaufwand, Verlustleistung, maximales Überschwingen von  $u_{ds}$  und Anzahl der Iterationen in Abhängigkeit von der Optimierung unterschiedlicher Harmonischer

# 4 Zusammenfassung und Ausblick

Leistungselektronische Wandler können elektromagnetische Störungen verursachen. Zur gezielten Ansteuerung der Leistungstransistoren und zur Reduktion der Störungen kann eine aktive Gate-Ansteuerung angewendet werden. Ausgehend von einer beliebig flexibel einstellbaren Gate-Spannung wird hier der Verlauf der Spannung mit dem Levenberg-Marquard-Verfahren optimiert. Ein Peak bei 35 MHz im Spektrum der Drain-Source Spannung eines durch Simulationen untersuchten Spannungswandlers sollte um 20 dB reduziert werden. Der Peak wird hervorgerufen durch eine gedämpfte Schwingung nach dem Ausschaltvorgang des Leistungstransistors. Bei einer breitbandigen Optimierung ist der Rechenaufwand extrem hoch, und eine Übertragung auf einen realen Spannungswandler scheint unmöglich. Deshalb wurde untersucht, ob gute Optimierungsergebnisse auch bei einer schmalbandigen Optimierung erzielt werden können. Betrachtet wurden das maximale Überschwingen der Drain-Source Spannung, die mittlere Verlustleistung

und des Konvergenzverhalten. Die schmalbandigen Optimierungen zeigen, dass eine deutliche Optimierung der Störaussendung möglich ist, und der Rechenaufwand erheblich reduziert werden kann.

In weiteren Untersuchungen soll das schmalbandige Optimierungsverfahren an einem Laboraufbau angewendet und analysiert werden. Dabei soll auch die Minimierung der Verlustleistung stärker in den Vordergrund rücken.

#### **Danksagung**

Dieser Beitrag entstand im Rahmen des Projekts VE4 (Vertrauenswürdige Entstörung von Energienetzen mittels echtzeitfähiger Edge-Komponenten) und wurde durch das BMBF (Bundesministerium für Bildung und Forschung) unter dem Förderkennzeichen 16ME0739 finanziell unterstützt. Die Verantwortung für den Inhalt dieses Beitrags liegt ausschließlich bei den Autoren.

#### Literatur

- [1] A. Lidow, M. De Rooij, J. Strydom, D. Reusch und J. Glaser, GaN transistors for efficient power conversion. Hoboken, NJ: Wiley, 2020, doi: 10.1002/9781119594406

- [2] J. Henn et al., "Intelligent gate drivers for future power converters", IEEE Trans.Power Electron., Bd. 37, Nr. 3, S. 77-87, März 2022, doi: 10.1109/TPEL.2021.3112337.

- [3] S. Zhao, X. Zhao, Y. Wie, Y.Zhao und H.A. Mantooth, "A review on switching slew rate control for silicon carbide devices using active gate drivers", *IEEE Journal of Emerging and Selected Topics in Power Electronics*, Bd. 9, Nr. 4, S. 4096-4114, 2021, doi: 10.1109/JESTPE.2020.3008344.

- [4] H. Takayama, S. Fukunaga and T. Hikihara, "Switching Trajectory Control of SiC MOSFET Based on I-V Characteristics Using Digital Active Gate Driver," 2021 IEEE 12th Energy Conversion Congress & Exposition - Asia (ECCE-Asia), Singapore, Singapore, 2021, S. 1338-1343, doi: 10.1109/ECCE-Asia49820.2021.9479118.

- [5] X. Huang, F. Wang, Y. Liu, F. Lin, H. Sun and Z. Yang, "Multi-Level Synthesis Gate Voltage Active Control Technology for Optimizing IGBT Switching Characteristics," in *IEEE Journal of Emerging and Selected Topics in Power Electronics*, Bd. 11, Nr. 3, S. 2918-2929, June 2023, doi: 10.1109/JESTPE.2022.3216277.

- [6] K. Miyazaki et al., "General purpose clocked gate driver IC with programmable 63-level drivability to optimize overshoot and energy loss in switching by simulated annealing algorithm", IEEE Trans. On Ind. Applicat., Bd. 53, Nr. 3, S. 2350-2357, Mai-Juni 2017, doi: 10.1109/TIA.2017.2674601.

- [7] Y.S. Cheng et al., "High speed searching of optimum switching pattern for digital active gate drive to adapt to various load conditions", *IEEE Transactions on Industrial Electronics*, Bd. 69, Nr. 5, S. 5185-5194, Mai 2022, doi: 10.1109/TIE.2021.3084169.

- [8] C. Krause, A. Bendicks und S. Frei, "Active gate control with synthesized signals to avoid overshoots and ringing in DC-to-DC converters", *PCIM Europe 2021*, Nürnberg, Deutschland, 03.-07.05.2021, S. 1256-1262.

- [9] D.J. Rogers und B. Murmann, "Digital active gate drives using sequential optimization", 2016 IEEE Applied Power Electronics Conference ans Exposition (APEC), Long Beach, CA, USA, S. 1650-1656, doi: 10.1109/APEC.2016.7468088.

- [10] C. Krause und S. Frei, "Narrowband Frequency Domain Optimized Gate Driving Signals for Power Transistors of DC/DC Converters", 2023 International Symposium on Electromagnetic Compatibility – EMC Europe, Krakow, Poland, 2023, S. 1-6, doi: 10.1109/EM-CEurope57790.2023.10274372

- [11] C. Krause, A. Bendicks und S. Frei, "Frequency-selective reduction of power electronic switsching noise by applying synthesized gate signals", *IEEE International Joint EMC/SI/PI and EMC Europe Symposium*, Raleigh, NC, USA, S. 100-105,2021, doi: 10.1109/EMC/SI/PI/EMCEurope52599.2021.9559190.

- [12] D. Schröder und M. Buss, Intelligente Verfahren. Berlin, Heidelberg: Springer Berlin Heidelberg, 2017, doi: 10.1007/978-3-662-55327-5.

- [13] Efficient Power Conversion Corporation, "EPC GaN Power Device Library", https://epc-co.com/epc/documents/spice-files/LTSPICE/EPCGaNLibrary.zip, 2021.